Technology

Digital Design Interview Questions | Combinational, Sequential, Clock Gating | Tasks | Functions

Creator: Flop_n_Adder

What You'll Learn

- Differentiate between combinational and sequential logic circuits, understanding their characteristics and applications.

- Explain clock gating and its benefits for power management in digital circuits, including its implementation and potential challenges.

- Distinguish between Verilog tasks and functions, outlining their syntax, capabilities, and appropriate use cases in digital design.

Video Breakdown

This video explains the differences between combinational and sequential logic, clock gating techniques for power management, and the distinction between Verilog tasks and functions. It provides Verilog code examples and discusses the benefits and challenges of each concept, offering valuable insights for digital design interviews.

Key Topics

Combinational vs Sequential

Clock Gating Technique

Dynamic Power Reduction

Verilog Task

Verilog Function

Timing Considerations

Video Index

Combinational vs. Sequential Logic

This module defines and differentiates combinational and sequential logic circuits, providing Verilo...

This module defines and differentiates combinational and sequential logic circuits, providing Verilog examples and highlighting their key differences in terms of output dependency, clock usage, memory, speed, and design complexity.

Understanding Combinational Logic

0:18 - 0:55

This chapter explains combinational logic circuits, their characteristics, and provides a Verilog code example.

Logic Gates

Current Inputs

No Clock

Understanding Sequential Logic

0:55 - 1:24

This chapter explains sequential logic circuits, their characteristics including memory, and provides a Verilog code example.

Memory Elements

Past Inputs

Flip-Flops

Key Differences Summarized

1:24 - 3:07

This chapter summarizes the key differences between combinational and sequential logic circuits across various aspects.

Output Dependency

Clock Presence

Memory

Examples

Clock Gating for Power Management

This module introduces clock gating as a power management technique, explaining its implementation, ...

This module introduces clock gating as a power management technique, explaining its implementation, benefits in reducing dynamic power dissipation, and the considerations for its use in digital circuit design.

Introduction to Clock Gating

3:07 - 3:49

This chapter introduces the concept of clock gating and its role in reducing power consumption.

Power Reduction

Switching Activity

Idle Circuits

Clock Gating Implementation

3:49 - 4:49

This chapter explains the implementation of clock gating with Verilog code and waveforms.

Verilog Code

Clock Enable

Gated Clock

Benefits and Challenges

4:49 - 6:03

This chapter discusses the benefits and challenges of implementing clock gating in digital designs.

Power Savings

Timing Impact

Verification

Verilog Tasks vs. Functions

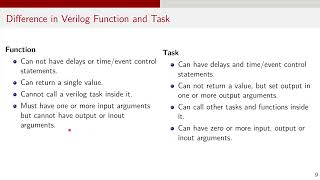

This module explains the differences between Verilog tasks and functions, covering their syntax, cap...

This module explains the differences between Verilog tasks and functions, covering their syntax, capabilities, and appropriate use cases, including examples and a summary of their key distinctions.

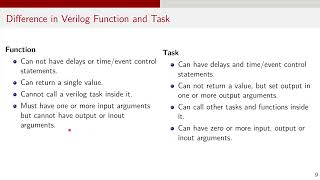

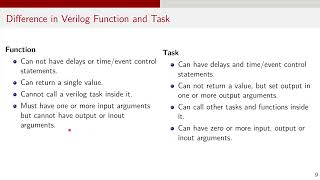

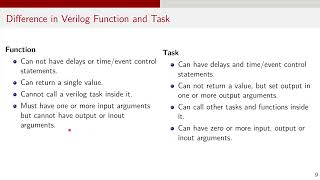

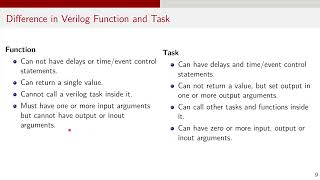

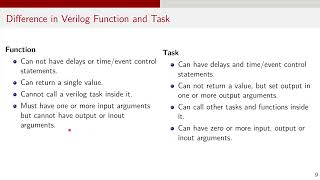

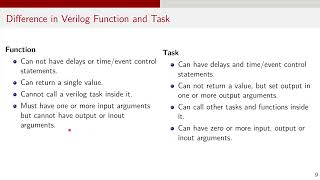

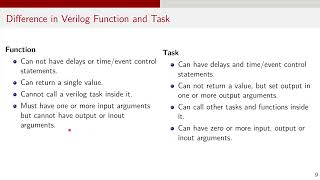

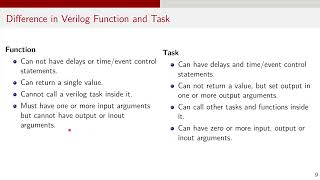

Understanding Verilog Functions

6:10 - 8:12

This chapter explains Verilog functions, their syntax, and limitations.

Return Value

Input Arguments

No Delays

Understanding Verilog Tasks

8:12 - 10:01

This chapter explains Verilog tasks, their syntax, and capabilities.

Output Arguments

Timing Delays

Complex Operations

Key Differences Summarized

10:01 - 10:53

This chapter summarizes the key differences between Verilog tasks and functions.

Timing Control

Return Value

Task Calling

Argument Types

Questions This Video Answers

What is the key difference between combinational and sequential logic?

Combinational logic's output depends solely on current inputs, while sequential logic's output depends on both current and past inputs, incorporating memory elements.

How does clock gating reduce power consumption?

Clock gating disables the clock signal to idle parts of a circuit, preventing unnecessary switching and reducing dynamic power dissipation.

When should I use a Verilog task versus a function?

Use functions for simple combinational logic with a single return value and no timing delays. Use tasks for more complex operations with timing delays, multiple outputs, or the need to call other tasks.

What are the benefits of clock gating?

Clock gating reduces dynamic power consumption, is scalable, and improves digital design efficiency.

Related Videos

Want to break down another video?

Break down another video